新一代铁电畴壁存储器(DWRAM)已被证明兼具非挥发性和ns级的读写速度、高密度存储的潜力,并且与现有硅基工艺兼容。对于快速读出电路,需要有大的驱动电流,基于LNO上的畴壁电流与电压满足一定非线性关系:I-V n,也就是说写入电流比读出电流大(~8个数量级),额外的功耗损失对于移动端的应用是很大的限制。理想的情况应该是很小的写入电流和较大的读出电流。

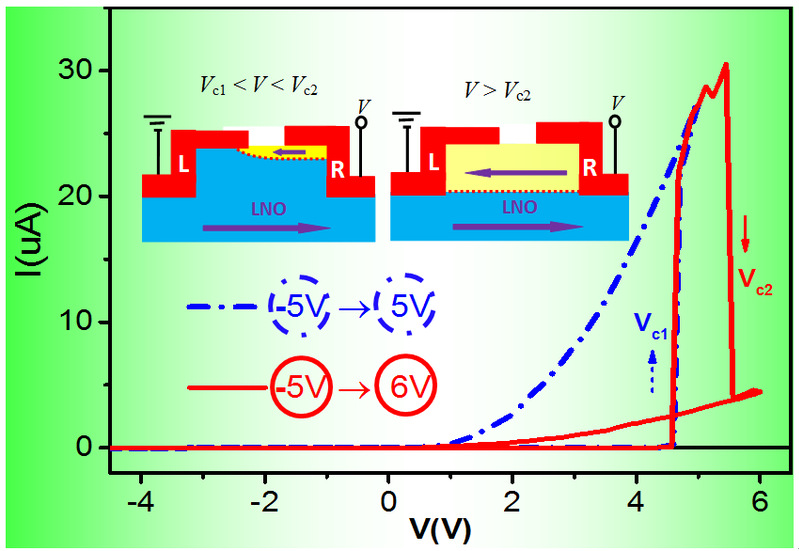

为了攻克这个难题,近日江安全团队通过控制电场分布,设计了一种较小写入电流、较大读出电流的LNO器件,如图1所示。通过电场控制电畴两次反转:第一次较小电场(V1<V<V2)形成稳定的头-头畴壁,具有很大电流通道;第二次较大电场(V>V2),形成不稳定的中性畴壁导电通道,电流较小,这时撤掉外电压就可以在较小电压下读到较大的电流。相关结果发表在ACS AMI,江钧和江安全老师为论文通讯作者,博士生汪超为论文第一作者。

图1 器件工作的I-V曲线图(内部为器件电畴反转示意图)

该项目得到上海市科技创新行动计划基础研究项目、国家重点研发计划、北京市自然科学基金和国家自然科学基金项目等专项资助。

原文链接,ACS AMI:https://pubs.acs.org/doi/full/10.1021/acsami.0c13534