会议时间:2017.10.12

会议地点:复旦大学微电子楼315室

会议主持:江安全研究员

会议主题:《下一代高性能通用铁电存储器》读写电路设计及键合工艺讨论会

参会人员:

江安全(研究员)、杨建国(博后)、白子龙(博士生)、张岩(博士生)、韩源源(博士生)、周可基(博士生)、柴晓杰(博士生)、连建伟(博士生)、郭会珍(硕士生)

会议内容:

一、方案

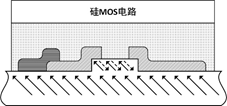

方案1:在LNO单晶片上键合基于硅薄膜的MOS电路,作为学术上的突破;

上世纪五、六十年代,IBM公司试图在铁电单晶片上制作存储器,但是由于电容式的铁电存储器需要上千伏电压才能使大单晶极化,加之当时加工工艺的限制,至今没有实现在单晶片上制造铁电存储器。使用面内读写结构可以在LNO单晶片表面雕刻图形,在上层的硅薄膜上制作读写电路,一旦成功在学术上有着重大的意义。

方案1示意图

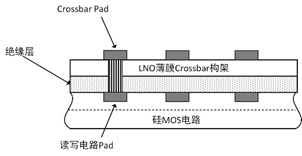

方案2:在硅基电路上键合LNO薄膜,在LNO薄膜上制造上下电极Crossbar结构的存储单元阵列。方案2也是最为重要的,是项目的重点,主要是用于批量生产。以下会议内容为方案2范畴。

大体设计要求:1、将读写电路的Pad设计到表面,便于通过接触孔与LNO薄膜上的Crossbar Pad接触。2、在读写电路上设计套刻标记,便于与上层的LNO薄膜对准。

方案2示意图

硅薄膜MOS电路流片,初步由中科院微电子所制作,如果有更好的CMOS流片厂家,可以考虑。

二、要求

1,前期在实验室里完成芯片制作。

2,LNO薄膜制作上下结构,构架为crossbar,尺寸为2 um×2 um,容量为1000 × 1000 = 1 M或者100×100 = 10K或者32×32 = 1K。

3,键合技术路线:

1要求下电极先制作在LNO上,键合在MOS电路上后,制作上电极。

2要求下电极先制作在MOS电路上表面,键合LNO薄膜后,制作上电极,并打孔连接到MOS电路上。将LNO薄膜键合在带有下电极的MOS电路上由中科院技物所沈宏老师完成,与韩源源和周可基博士合作,先摸索在设计有Pad电极的硅片上键合LNO薄膜工艺。

4,MOS电路的流片,我们计划在4英寸圆片上制作芯片,需要将流片的8英寸切出4英寸圆片电路,读写电路的设计要在4英寸的圆片内设计,使用的是0.18 um工艺。

三、细节

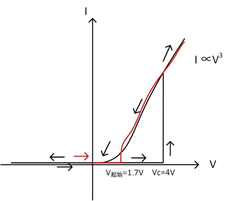

由于印刻效应的存在,写入时间为5 ms。写入电压Vwrite = 5 V (将来可能实现3V写入电压),读取时间不限,读取电压Vread = 2 ~ 3 V,读取电流在100 nA~1 uA,单元尺寸2 um。(其关态电流Ioff可以达到1 pA)。

四、建议

1,杨建国博士:1T1R 译码方式与Crossbar译码方式不同,1T1R译码更为简单,1T1R构架需要将每个存储单元上连接一个晶体管,通过字线控制晶体管开关。会议采纳其建议,将这两种译码方式一起纳入设计方案内。

2,周可基博士:需要2 um尺寸的电容参数。制作好器件后立马将电容的测试结果反馈给电路设计。

3,韩源源和周可基博士:I/O接口只可输出3.3V的电压,无法满足5V的需求,杨博士提出I/O可输出5V的电压,并且在后续工作中,随着器件性能的提升写入电压可能在3.3V以下,写入电压可以通过外部控制。

4,读写电路设计write in/read out 可以异步实现。